在人工智能技术飞速发展的浪潮中,如何构建高效、可靠、可扩展的AI系统,已成为学术界和产业界共同关注的核心问题。杜克大学电子与计算机工程系教授陈怡然长期致力于高效人工智能系统的软硬件协同设计研究,为人工智能基础软件的开发指明了关键路径。他的工作深刻揭示了,在AI从算法创新走向大规模应用落地的过程中,跨越软硬件之间的“语义鸿沟”,实现系统层面的深度协同优化,是释放算力潜能、推动AI普惠的关键。

一、 效能瓶颈与协同设计理念的兴起

当前,人工智能,特别是深度学习,正面临显著的“效能墙”挑战。一方面,摩尔定律逐渐放缓,通用处理器(如CPU)的性能提升难以匹配AI模型对算力指数级增长的需求。另一方面,AI模型变得日益庞大和复杂,从千亿参数的大语言模型到多模态模型,其计算、存储和通信开销巨大。单纯依靠硬件工艺进步或算法层面的优化,已无法经济、高效地满足实际部署需求。

正是在此背景下,陈怡然教授倡导的“软硬件协同设计”理念展现出巨大价值。这一理念的核心在于,打破传统上硬件设计与软件开发分离的藩篱,在系统设计的初始阶段,就综合考虑算法特性、编程模型、编译器优化、体系结构乃至芯片电路等多个层次的需求与约束。其目标不是让软件去适应固定的硬件,也不是让硬件盲目追求峰值算力,而是让两者在定义、设计和优化过程中深度互动,共同寻找到在特定应用场景下性能、能效、成本、灵活性的最优平衡点。

二、 协同设计驱动的基础软件栈革新

人工智能基础软件栈,包括框架(如TensorFlow, PyTorch)、编译器(如TVM, MLIR)、运行时系统、驱动等,是连接上层AI应用与底层硬件的桥梁。陈怡然教授的研究指出,协同设计必须深刻影响这一软件栈的各个层级。

- 计算图与中间表示(IR)的协同:现代AI框架将计算表达为数据流图。协同设计要求编译器能够理解并优化这种高级抽象,将其映射到目标硬件的高效原语上。例如,设计硬件友好的中间表示,能够同时捕获算法的计算模式与硬件的并行、存储层次特性,为后续的自动化优化(如算子融合、内存规划、流水线调度)奠定基础。

- 自动代码生成与优化:针对专用AI加速器(如ASIC、FPGA)多样化的指令集和内存架构,传统手写高性能内核的方式成本高昂且不可持续。协同设计推动编译器技术向自动化、智能化发展,能够根据硬件描述和算法子图,自动搜索并生成接近手工优化性能的代码,极大地提升了开发效率和硬件的适配范围。

- 运行时系统的资源协同管理:在分布式训练或边缘推理场景中,任务调度、内存分配、通信同步等运行时决策对整体效能至关重要。协同设计的运行时系统能够感知底层硬件的拓扑结构、带宽和计算单元状态,与框架的并行策略相结合,实现动态的、自适应的资源管理,以最小化端到端的延迟和能耗。

三、 面向新兴挑战的协同设计前沿

陈怡然教授的研究也前瞻性地布局于一系列新兴方向,这些方向正在重塑高效AI系统设计的未来:

- 稀疏性与非规则计算:模型压缩(如剪枝、量化)产生的稀疏模型,以及图神经网络等非规则计算模式,对传统的规则并行硬件架构提出了挑战。协同设计需要开发新的稀疏表示格式、专用硬件单元(如稀疏张量核心)以及配套的软件调度策略,以高效利用稀疏性带来的收益。

- 内存与存储层级优化:AI模型的规模常常受限于内存容量和带宽。通过协同设计,可以在算法层面(如激活检查点技术)、编译器层面(如计算重排序以提升数据局部性)和硬件层面(如设计高带宽内存、近存计算架构)进行联合创新,突破“内存墙”限制。

- 安全、可靠与隐私的协同考量:高效性不能以牺牲安全性为代价。协同设计需要将对抗鲁棒性、隐私保护(如联邦学习中的安全聚合)、硬件可信执行环境等需求,早期纳入软硬件设计的权衡中,构建高效且可信的AI系统。

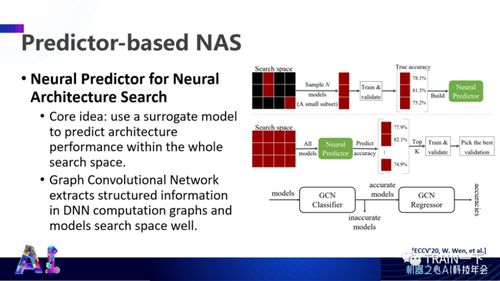

- 敏捷开发与设计空间探索:为了快速应对多样化的AI应用,需要建立基于高层抽象(如领域特定语言)的敏捷开发流程和工具链。协同设计方法结合机器学习技术,可以自动化地在大规模的软硬件设计空间中进行快速探索与评估,加速从概念到高效实现的周期。

杜克大学陈怡然教授在高效人工智能系统软硬件协同设计方面的深入研究,阐明了人工智能基础软件开发的下一个范式转变。它告诉我们,未来的AI竞争力不仅在于更精巧的算法模型,更在于构建一个从应用、软件到硬件的垂直整合、紧密协同的优化体系。这要求研究者与工程师具备跨层次的系统思维,共同推动基础软件栈的革新,从而为人工智能在更广阔领域的深入应用,铺设一条高效、节能且普惠的道路。软硬件协同设计,正从一项前沿技术理念,演进为构筑下一代人工智能基础设施的核心方法论。